Deweloperzy projektujący zaawansowane aplikacje sterowania wbudowanego mogą skorzystać z nowego kontrolera dsPIC® wyposażonego w dwa rdzenie w jednym układzie. Nowe kontrolery dsPIC33CH, dzięki swoim unikalnym właściwościom, umożliwią łatwiejszą integrację oprogramowania dla zaawansowanych aplikacji wbudowanych wymagających wyrafinowanych algorytmów. W architekturze Master-Slave zastosowanej w kontrolerach dsPIC33CH, rdzeń podrzędny służy do wykonywania dedykowanego, krytycznego kodu sterującego, podczas gdy główny rdzeń zajęty jest obsługą działania interfejsu użytkownika, monitorowaniem systemu i funkcji komunikacyjnych, dostosowanych do potrzeb aplikacji końcowej.

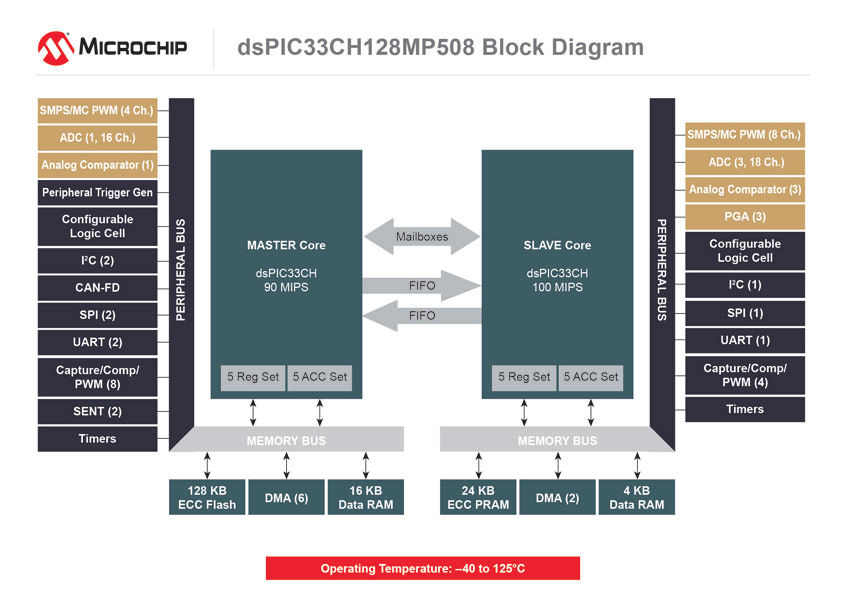

Urządzenia z rodziny dsPIC33CH to pierwsze dwurdzeniowe, 16-bitowe kontrolery DSC firmy Microchip. Układ dsPIC33CH128MP508 posiada dwa rdzenie o wydajności 90 MIPS dla rdzenia Master oraz 100 MIPS dla Slave, które mogą pracować niezależnie. Rodzina dsPIC33CH zapewnia bezprecedensowy w branży stopień integracji urządzeń peryferyjnych oraz interfejsów komunikacyjnych w pakiecie o wielkości zaledwie 5x5 mm. Dlatego aby obniżyć rozmiar oraz całkowite koszty systemu, dla każdego rdzenia dostępne są niezależnie zaawansowane urządzenia peryferyjne, w tym m.in. szybkie konwertery analogowo-cyfrowe ADC 12-bit 3.5 MSPS, przetworniki cyfrowo-analogowe DAC z generowaniem fal, komparatory analogowe, analogowe programowalne wzmacniacze zysku oraz sprzętowa modulacja szerokości impulsu (PWM). Jako pierwsza rodzina dsPIC33 dysponuje również obsługą przemysłowej klasy, wydajnego interfejsu CAN-FD.

Więcej informacji o nowej rodzinie kontrolerów DSC dsPIC33CH firmy Microchip mogą Państwo uzyskać w dokumentacji technicznej. Zapraszamy również do kontaktu z naszym działem handlowym.

Kontrolery dsPIC33CH

Główne cechy rodziny dsPIC33CH

- Dwurdzeniowy 16-bitowy mikrokontroler dsPIC33CH

- Master Core 90 MIPS and Slave Core 100 MIPS Operation

- Independent Peripherals for Master Core and Slave Core

- Configurable Shared Resources for Master Core and Slave Core

- Fast 6-Cycle Divide

- Message Boxes and FIFO to Communicate Between Master and Slave (MSI)

- Code Efficient (C and Assembly) Architecture

- 40-Bit Wide Accumulators

- Single-Cycle (MAC/MPY) with Dual Data Fetch

- Single-Cycle, Mixed-Sign MUL Plus Hardware Divide

- 32-Bit Multiply Support

- Five Sets of Interrupt Context Selected Registers and Accumulators per Core for Fast Interrupt Response

- Zero Overhead Looping

- Wysokiej wydajności urządzenia peryferyjne dla kontroli w czasie rzeczywistym

- 4 x 12-bit 3.5 MSPS ADCs

- High Speed PWMs with 250ps resolution, 12 Ch

- Optimized for high-performance digital power, motor control and applications requiring sophisticated algorithms

- Cechy rdzenia Master

- Core Frequency 90 MIPS @ 180 MHz

- Internal Data RAM: 16 Kbytes

- 16-Bit Timer: 1

- DMA: 6

- SCCP (Capture/Compare/Timer): 8

- UART: 2

- SPI/I2S: 2

- I2C: 2

- CAN Flexible Data-Rate (FD): 1

- SENT: 2

- CRC: 1

- QEI: 1

- PTG:1

- CLC: 4

- 16-Bit High-Speed (250ps) PWM: 4

- 12-bit, 3.5 Msps ADC: 1

- Digital Comparator: 4

- 12-Bit DAC/Analog CMP Module: 1

- Watchdog Timer: 1

- Deadman Timer: 1

- Breakpoints: 3 complex, 5 simple

- Oscillator: 1

- Cechy rdzenia Slave

- Core Frequency 100 MIPS @ 200 MHz

- Program Memory: 24 Kbytes (PRAM) Dual Partition with LiveUpdate

- Internal Data RAM: 4 Kbytes

- 16-Bit Timer: 1

- DMA: 2

- SCCP (Capture/Compare/Timer): 4

- UART: 1

- SPI/I2S: 1

- I2C: 1

- QEI: 1

- CLC: 4

- 16-Bit High-Speed (250ps) PWM: 8

- 12-bit, 3.5 Msps ADC: 3

- Digital Comparator: 4

- 12-Bit DAC/Analog CMP Module: 3

- Watchdog Timer: 1

- Breakpoints: 1 complex, 2 simple

- Oscillator: 1

- Zarządzanie zegarem

- Internal Oscillator

- Programmable PLLs and Oscillator Clock Sources

- Master Reference Clock Output

- Slave Reference Clock Output

- Fail-Safe Clock Monitor (FSCM)

- Fast Wake-up and Start-up

- Backup Internal Oscillator

- LPRC Oscillator

- Zarządzanie mocą

- Low-Power Management Modes (Sleep, Idle, Doze)

- Integrated Power-on Reset and Brown-out Reset

- Wsparcie deweloperskie

- In-Circuit and In-Application Programming

- Simultaneous Debugging Support for Master and Slave Cores

- Master Only Debug and Slave Only Debug Support

- IEEE 1149.2 Compatible (JTAG) Boundary Scan

- Trace Buffer and Run-Time Watch

- Warunki pracy

- Zakres napięcia roboczego od 3V do 3.6V

- Zakres temperatury pracy od -40°C do +125°C

Komentarze do artykułu